- 畅销套餐

- 精选套餐

- 人气套餐

- 尊享套餐

- 高薪套餐

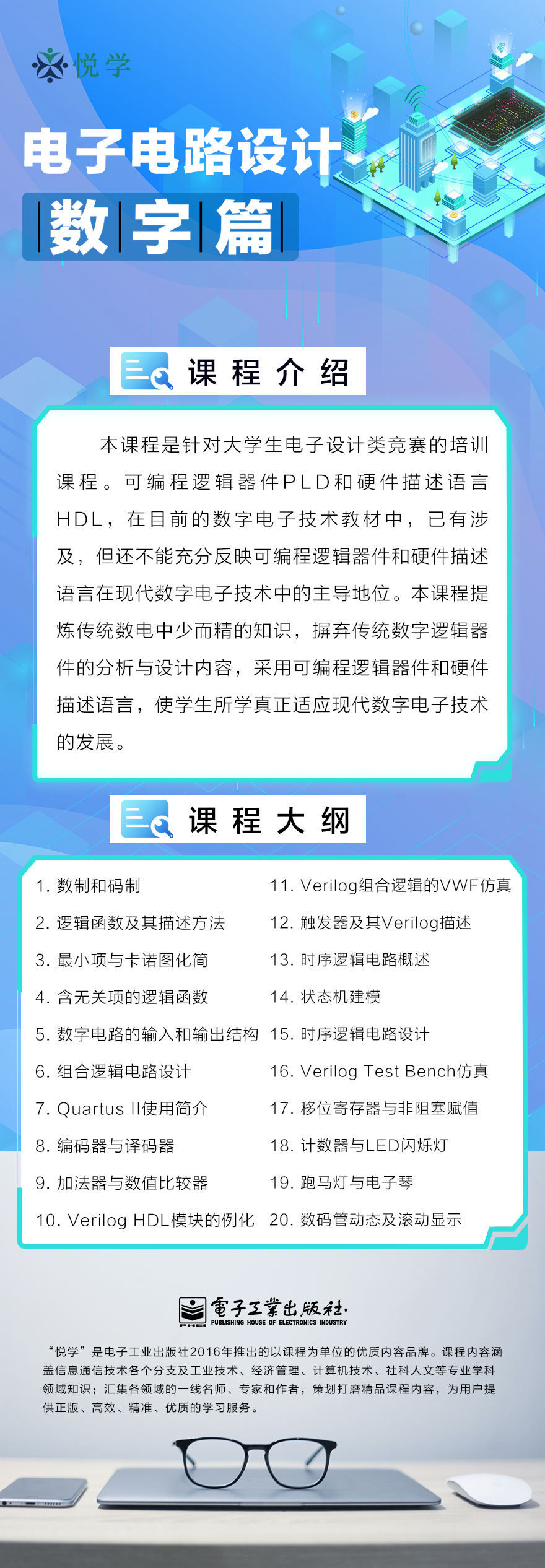

- 课程介绍

- 课程大纲

适合人群:

对电子电路设计感兴趣的学生及从业人员

你将会学到:

让学生可以把创意和想法高效的变成现实

课程简介:

本课程是针对大学生电子设计类竞赛的培训课程。可编程逻辑器件PLD和硬件描述语言HDL,在目前的数字电子技术教材中,已有涉及,但还不能充分反映可编程逻辑器件和硬件描述语言在现代数字电子技术中的主导地位。“电子电路设计(数字篇)”课程,将提炼传统数电中少而精的知识,摒弃传统数字逻辑器件的分析与设计内容,采用可编程逻辑器件和硬件描述语言,使学生所学真正适应现代数字电子技术的发展。

课程大纲-电子电路设计 数字篇

5

数字电路的输入和输出结构不同种类数字IC的输入电平门限,输出电平极限值是不同的。CMOS芯片的噪声门限大于TTL芯片。介绍了三种典型的数字芯片输出结构,包括强1强0的图腾柱、三态门和强0弱1的OC/OD门。

「仅限付费用户」点击下载“数字电路的输入和输出结构.pptx”

[16:12]开始学习7

Quartus II使用简介PLD的种类包括CPLD和FPGA。介绍了Cyclone IV与Qaurtus II 14.1的关系,在Quartus中如何新建工程,module开始,endmodule结尾的模块代码举例,编译Verilog HDL工程文件并查看RTL设计。

「仅限付费用户」点击下载“Quartus II使用简介.pptx”

[09:49]开始学习10

Verilog HDL模块的例化对于简单数字电路,可以由单一模块编写硬件描述语言代码。但是复杂的数字电路中,总是包含很多现有模板。使用若干现有模块构造新模块称为模块的例化。

「仅限付费用户」点击下载“Verilog HDL模块的例化.pptx”

[07:45]开始学习11

Verilog组合逻辑的VWF仿真在Verilog HDL代码编译通过以后,需要验证代码功能正确。可以选择仿真或者是下载代码到芯片实际检测。复杂代码很难一次成功,进行仿真的意义重大,仿真代码的长度往往比模块代码更长。本次课先介绍最简单的一种仿真方法,quartus自带的波形仿真VWF(Vector Waveform File)。

「仅限付费用户」点击下载“Verilog组合逻辑的VWF仿真.pptx”

[06:42]开始学习12

触发器及其verilog描述介绍了几种常用触发器及其verilog描述,包括SR锁存器、D触发器、JK触发器

「仅限付费用户」点击下载“触发器及其verilog描述.pptx”

[19:38]开始学习16

Verilog Test Bench仿真VWF波形图仿真仅能“制造”出很有限的激励波形,无法满足复杂仿真需求。在Quartus II中14.1版本(因大学计划保留)是之后支持VWF仿真的版本。在安装verilog软件时,安装过一个ModleSim-Altera软件,这是ModleSim的免费版本,可提供Test Bench全功能仿真(比收费版速度稍慢)。

「仅限付费用户」点击下载“Verilog Test Bench仿真.pptx”

[11:28]开始学习17

移位寄存器与非阻塞赋值主要介绍了移位寄存器的结构和功能,阻塞赋值与非阻塞赋值的区别,阻塞赋值对赋值顺序有要求,非阻塞赋值在过程块内顺序无要求。

「仅限付费用户」点击下载“移位寄存器与非阻塞赋值.pptx”

[10:55]开始学习18

计数器与LED闪烁灯计数器主要用于计数、分频、定时、产生节拍脉冲等。列举了其典型应用案例,基于晶振分频时钟信号的闪烁灯。

「仅限付费用户」点击下载“计数器与LED闪烁灯.pptx”

[14:14]开始学习20

数码管动态及滚动显示本节课将介绍基于计数器的数码管显示。通过产生一个刷新时钟(计数器),实现数码管动态显示。通过增加一个更低频率的位移时钟(计数器),实现滚动显示。

「仅限付费用户」点击下载“数码管动态及滚动显示.pptx”

[11:10]开始学习

“悦知大学”老师的其他课程更多+

下载学堂APP缓存视频离线看

下载学堂APP缓存视频离线看