- 课程介绍

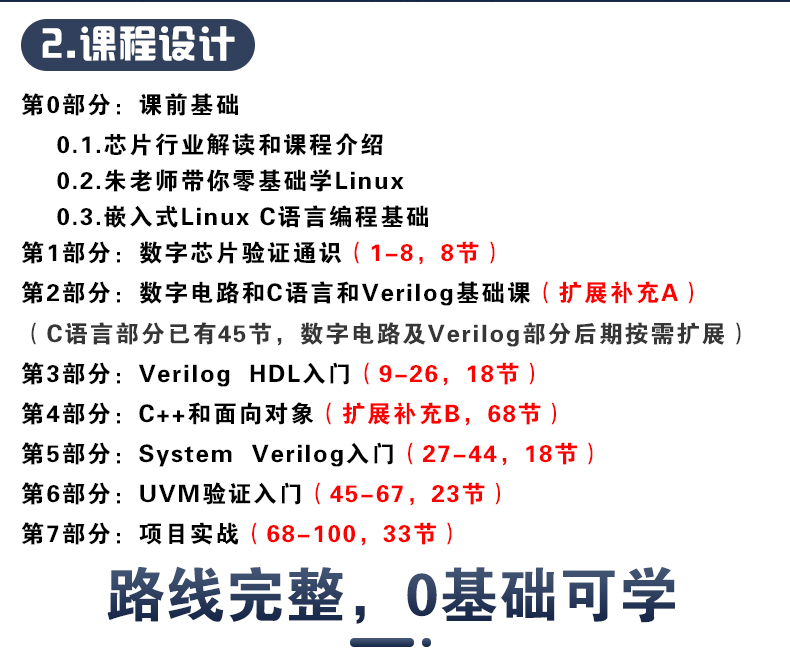

- 课程大纲

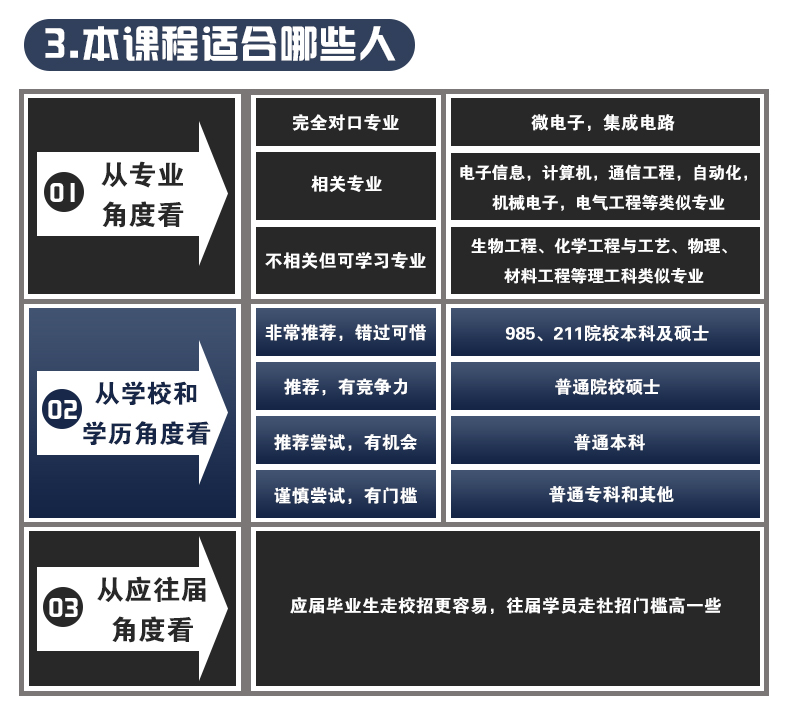

适合人群:

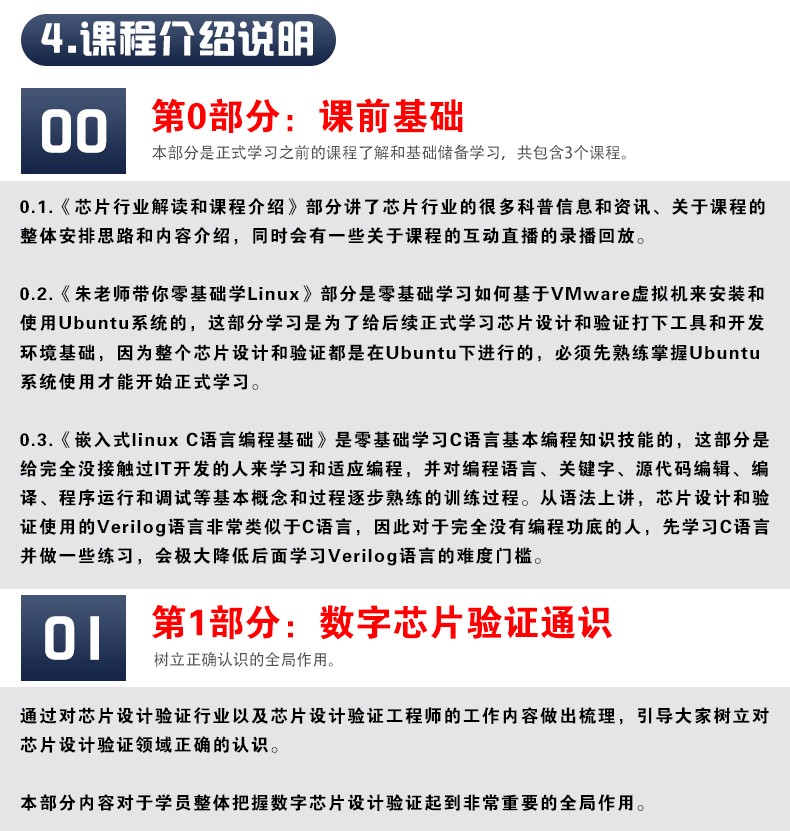

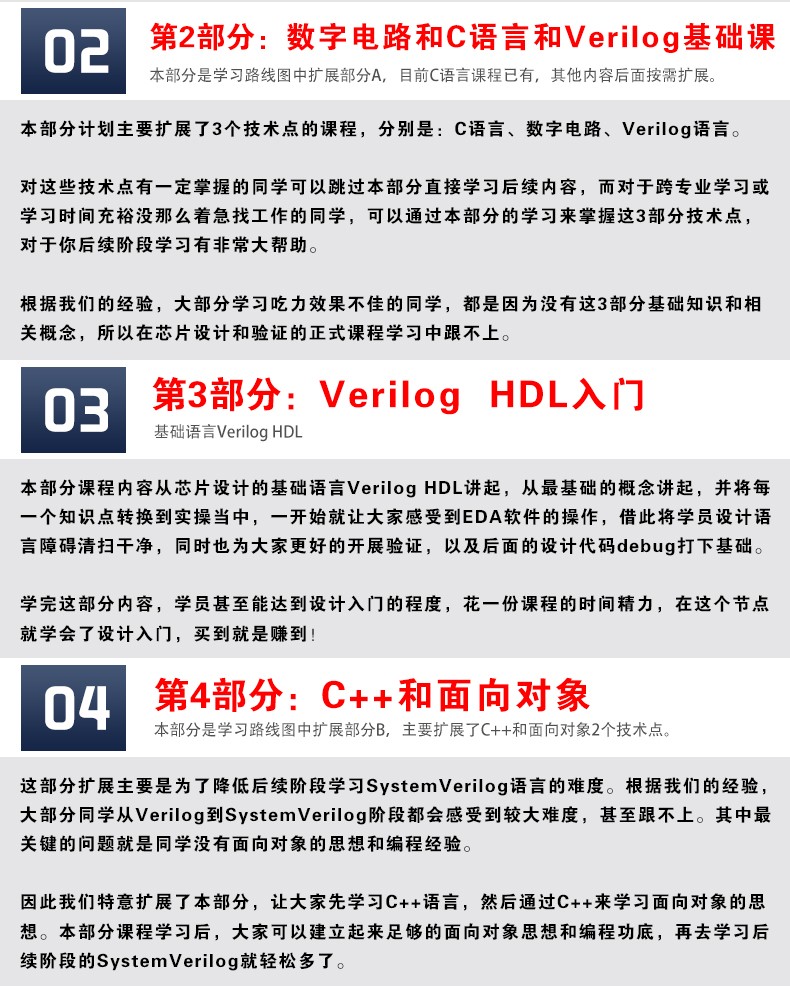

本课程扩展是为了降低后续阶段学习SystemVerilog语言的难度,可以考虑先学C++语言,建立面向对象思想;此课程并非零基础,适合有C语言基础,尤其是学过嵌入式课程的《C语言专题精讲篇》的同学。

你将会学到:

建立起来足够的面向对象思想和编程功底,为后续阶段学习SystemVerilog打下基础。

- 通过C++来学习面向对象的思想

- 建立起来足够的面向对象思想和编程功底,能更轻松学习后续的SystemVerilog

课程简介:

如果有C++基础或者之前有学习过朱老师的C++课程,可以跳过本部分内容。

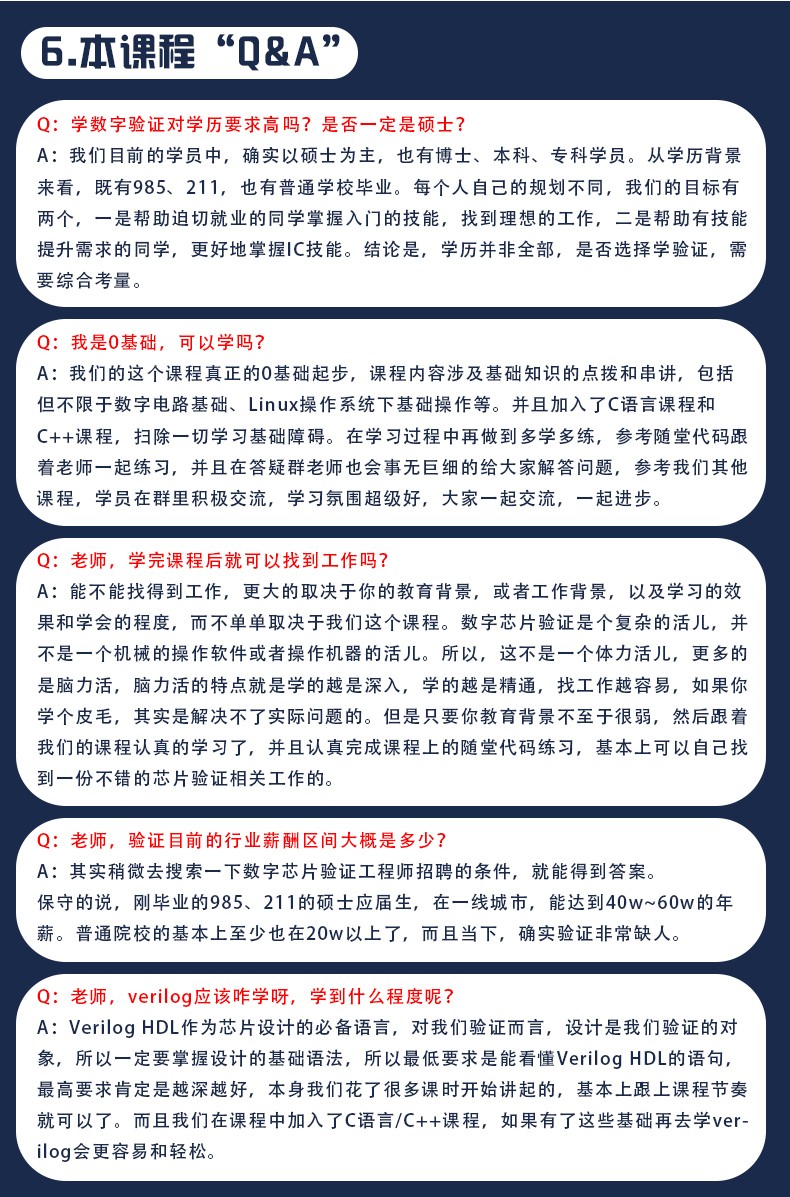

常见问题:

问:Q:老师,verilog应该咋学呀,学到什么程度呢?

答:A:Verilog HDL作为芯片设计的必备语言,对我们验证而言,设计是我们验证的对象,所以一定要掌握设计的基础语法,所以低要求是能看懂Verilog HDL的语句,高要求肯定是越深越好,本身我们花了很多课时开始讲起的,基本上跟上课程节奏就可以了。而且我们在课程中加入了C语言/C++课程,如果有了这些基础再去学verilog会更容易和轻松。

问: Q:我是0基础,可以学吗?

答:A:我们的这个课程真正的0基础起步,课程内容涉及基础知识的点拨和串讲,包括但不限于数字电路基础、Linux操作系统下基础操作等。并且加入了C语言课程和C++课程,扫除一切学习基础障碍。在学习过程中再做到多学多练,参考随堂代码跟着老师一起练习,并且在答疑群老师也会事无巨细的给大家解答问题,参考我们其他课程,学员在群里积极交流,学习氛围超级好,大家一起交流,一起进步。

课程大纲-C++和面向对象--数字芯片验证第4部分(扩展补充B)

第1章B1.为什么会有C++这门语言(2小时11分钟5节)

第2章B2.C++开发环境搭建(1小时1分钟3节)

第3章B3.C++基本编程体验(4小时44分钟10节)

第4章B4.会C语言就能学会面向对象(2小时55分钟7节)

“朱有鹏”老师的其他课程更多+

下载学堂APP缓存视频离线看

下载学堂APP缓存视频离线看