B3.02.namespace的初级定义和使用

{{ interaction.likeNum == 0 ? (pageType === 'video' ? '抢首赞' : '点赞') : formatNumber(interaction.likeNum) }}

{{ interaction.collectionNum == 0 ? '收藏' : formatNumber(interaction.collectionNum) }}

{{ interaction.discussNum == 0 ? (pageType === 'video' ? '抢沙发' : '讨论') : formatNumber(interaction.discussNum) }}

分享

适合人群

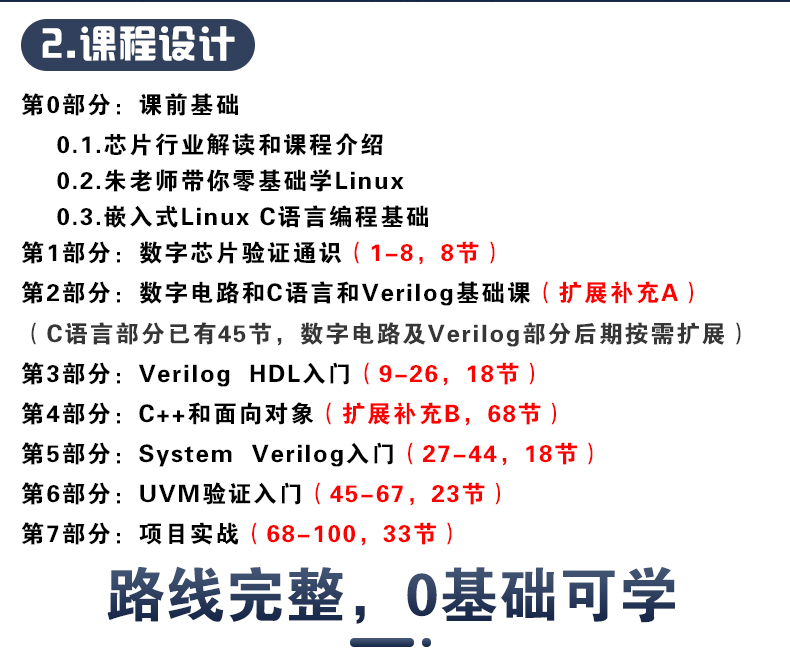

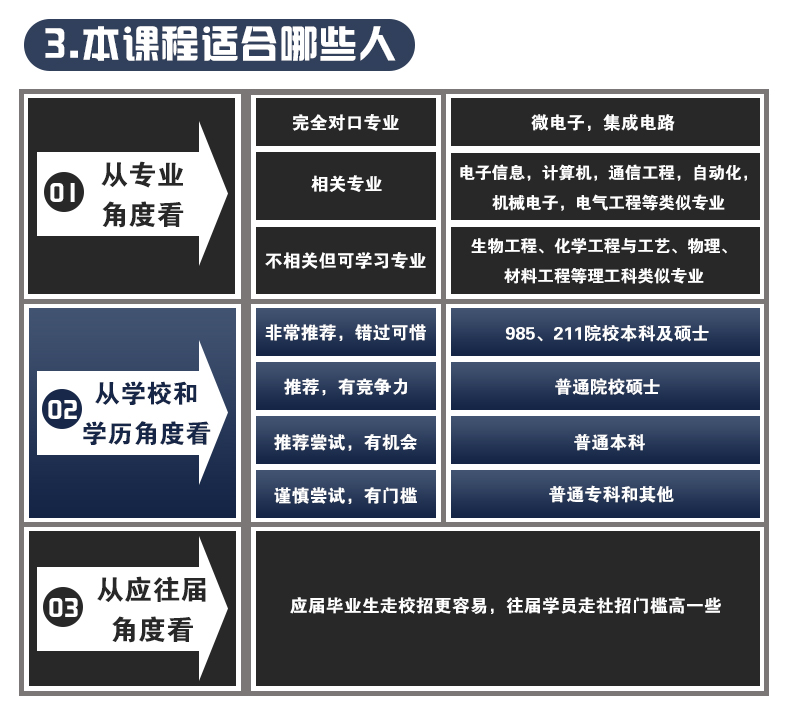

本课程扩展是为了降低后续阶段学习SystemVerilog语言的难度,可以考虑先学C++语言,建立面向对象思想;此课程并非零基础,适合有C语言基础,尤其是学过嵌入式课程的《C语言专题精讲篇》的同学。

你将会学到

建立起来足够的面向对象思想和编程功底,为后续阶段学习SystemVerilog打下基础。

- 通过C++来学习面向对象的思想

- 建立起来足够的面向对象思想和编程功底,能更轻松学习后续的SystemVerilog

课程简介

如果有C++基础或者之前有学习过朱老师的C++课程,可以跳过本部分内容。

常见问题

问:Q:老师,verilog应该咋学呀,学到什么程度呢?

答:A:Verilog HDL作为芯片设计的必备语言,对我们验证而言,设计是我们验证的对象,所以一定要掌握设计的基础语法,所以低要求是能看懂Verilog HDL的语句,高要求肯定是越深越好,本身我们花了很多课时开始讲起的,基本上跟上课程节奏就可以了。而且我们在课程中加入了C语言/C++课程,如果有了这些基础再去学verilog会更容易和轻松。

问: Q:我是0基础,可以学吗?

答:A:我们的这个课程真正的0基础起步,课程内容涉及基础知识的点拨和串讲,包括但不限于数字电路基础、Linux操作系统下基础操作等。并且加入了C语言课程和C++课程,扫除一切学习基础障碍。在学习过程中再做到多学多练,参考随堂代码跟着老师一起练习,并且在答疑群老师也会事无巨细的给大家解答问题,参考我们其他课程,学员在群里积极交流,学习氛围超级好,大家一起交流,一起进步。

展开更多

{{tips.text}}

{{ noteHeaderTitle }}

笔记{{ hasMyNote ? '我的笔记' : '记笔记' }}

{{ hasMyNote ? '我的笔记' : '记笔记' }}

优质笔记

更新于:{{ $dayjs.formate('YYYY-MM-DD HH:mm:ss', item.last_uptime*1000) }}

公开笔记对他人可见,有机会被管理员评为“优质笔记”

{{ noteEditor.content.length }}/2000

公开笔记

保存提问

讲师收到你的提问会尽快为你解答。若选择公开提问,可以获得更多学员的帮助。

记录时间点

记录提问时视频播放的时间点,便于后续查看

公开提问

提交课程大纲

自动连播

- 第一章 B1.为什么会有C++这门语言

- 1-1试看 B1.1.朱老师C++课程整体介绍35:35

- 1-2试看 B1.2.为什么有了C还需要C++26:56

- 1-3B1.3.C++究竟是个怎样的语言27:28

- 1-4B1.4.C++的典型项目和优势领域15:06

- 1-5B1.5.C++程序员发展前景分析26:42

- 第二章 B2.C++开发环境搭建

- 2-1B2.1.如何选择合适的开发环境16:56

- 2-2B2.2.常用C++开发环境介绍25:36

- 2-3B2.3.Linux命令行下C++编程初体验18:52

- 第三章 B3.C++基本编程体验

- 3-1B3.01.何为命名空间31:16

- 3-2B3.02.namespace的初级定义和使用32:51

24课时

24课时C++新增和有变化的关键字-1部分第4课

5493人学习

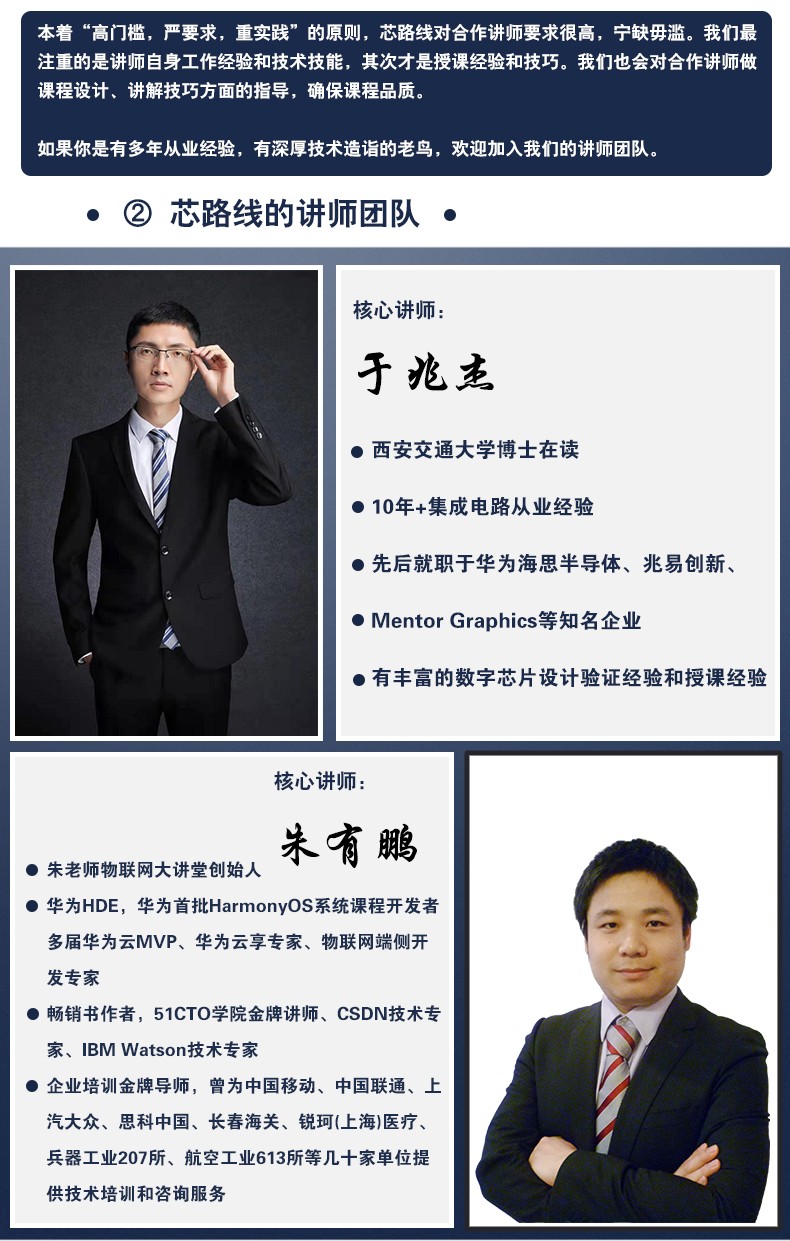

朱有鹏

5.0

¥69.00

22课时

22课时C++继承和多态特性-第2部分第3课

5094人学习

朱有鹏

5.0

¥59.00

17课时

17课时C++的封装和访问权限-第2部分第2课

4374人学习

朱有鹏

5.0

¥59.00

15课时

15课时C++基本编程体验-1部分第3课

3952人学习

朱有鹏

5.0

¥39.00

15课时

15课时STL的容器类和迭代器-第3部分第2课

2348人学习

朱有鹏

5.0

¥59.00

11课时

11课时C++模板编程入门-第3部分第1课

2331人学习

朱有鹏

5.0

¥39.00

5课时

5课时为什么会有C++这门语言-1部分开篇

1626人学习

朱有鹏

5.0

会员免费

7课时

7课时会C语言就能学面向对象-第2部分开篇

1515人学习

朱有鹏

5.0

会员免费